SPxDT_CFG( SPORTx DMA Transmit Configuration )はSPORT 送信DMAの設定を行います。

SPORTが3系統あるため、SP0DT_CFG、SP1DT_CFG、SP2DT_CFGの三本が用意されています。

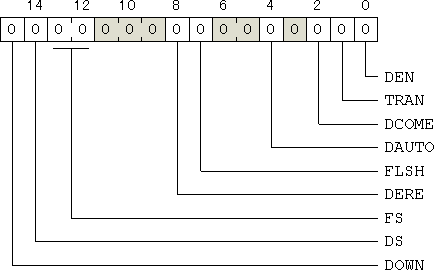

このレジスタは図1のような構造をもっています。初期値は0です。

図1 レジスタの構造

各ビットの意味は以下のとおりです。

DMAを有効にします。

転送方向を決めます。このビットはデスクリプターDMAの場合、デスクリプタからのロードでだけ設定できます。

ブロック転送後の割り込みの有無を決めます。このビットはデスクリプタDMAではデスクリプタからのロードでだけ設定できます。

DMAをオートバッファーDMAに変更します。

直前のDMA転送が失敗に終ったとき、バッファをクリアするために使います。

ブロック転送時のエラーによる割り込みの有無を決めます。このビットはデスクリプターDMAの時にはデスクリプタからのロードでだけ設定できます。

FIFOの状態をあらわします。

DMAの終了ステータスです。

デスクリプターDMAでDMAデスクリプタのオーナーをあらわします。このステータスはメモリー上のデスクリプタにも反映されます。

C/C++言語用に以下のインターフェースが用意されています。宣言はsysreg.hで行われています。SPxDT_CFGにアクセスする前には必ずIOPGにSPORTx_Control_Pageを設定してください。SPORTはポートごとにIOページが異なりますので注意が必要です。

SPORT0の場合は以下のとおりです。

// #include <sysreg.h> // #include <def2191.h> sysreg_write(sysreg_IOPG, SPORT0_Controller_Page) // SPORT0ページに設定 io_space_write(SP0DT_CFG, 値) // SP0DT_CFGに値を設定 変数 = io_space_read(SP0DT_CFG) // SP0DT_CFGの値を取得

SPORT1の場合は以下のとおりです。

// #include <sysreg.h> // #include <def2191.h> sysreg_write(sysreg_IOPG, SPORT1_Controller_Page) // SPORT1ページに設定 io_space_write(SP1DT_CFG, 値) // SP1DT_CFGに値を設定 変数 = io_space_read(SP1DT_CFG) // SP1DT_CFGの値を取得

SPORT2の場合は以下のとおりです。

// #include <sysreg.h> // #include <def2191.h> sysreg_write(sysreg_IOPG, SPORT2_Controller_Page) // SPORT2ページに設定 io_space_write(SP2DT_CFG, 値) // SP2DT_CFGに値を設定 変数 = io_space_read(SP2DT_CFG) // SP2DT_CFGの値を取得

アナログデバイセズが配布しているmcmの中のビット定義ファイルdef2191bit.hから関連するビット定義部分をここに引用します。

// Definition for DMA_CFG of commond operation

// HISTORY of CHNGE FS_xxx is fixed

#define DOWN BIT_15

#define DS BIT_14

#define FS_OFST 12

#define FS_MASK ( 3 << FS_OFST )

#define FS_EMPTY ( 0 << FS_OFST )

#define FS_ONE_WORD ( 1 << FS_OFST )

#define FS_TWO_WORD ( 2 << FS_OFST )

#define FS_THREE_WORD ( 3 << FS_OFST )

#define DERE BIT_8

#define FLSH BIT_7

#define DAUTO BIT_4

#define DTYPE BIT_3

#define DCOME BIT_2

#define TRAN BIT_1

#define DEN BIT_0

| 項目 | マニュアルのページ等 |

|---|---|

| 説明 | HR B-44 |

| DMAの解説 | HR 6-1 |

| SPORT DMA | HR 6-16 |

| DMA パッキング | HR 9-36 |