SPx_MCMC2 ( SPORTx Multi-Channel Configuration 2 )レジスタは、シリアルポートのマルチチャンネル動作を設定するための16ビットレジスタです。このレジスタは送受兼用です。

SPORTが3系統あるため、SP0_MCMC2、SP1_MCMC2、SP2_MCMC2の三本が用意されています。

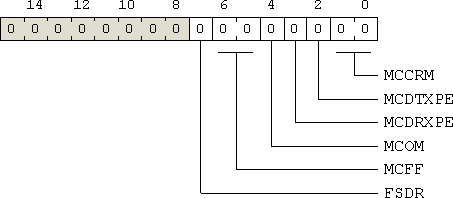

このレジスタは16ビットレジスタです。リセット後は0に初期化されます。図1にレジスタの構造を示します。

図1 レジスタの構造

以下に各フィールドの説明を行います。値はSPORTがディセーブルのときにだけ変更できます。

クロック再生モードを指定します。

マルチチャンネルモードにおいて送信DMAのパッキングを有効にします。

マルチチャンネルモードにおいて受信DMAのパッキングを有効にします。

チャンネル番号と物理チャンネルの間のマッピングを制御します。この設定はSPx_MTCSyとSPx_MRCSyの動作に影響を与えます。

マルチチャンネル動作時にDMAが何チャンネル分のプリフェッチを行うかを指定します。

これはH.100プロトコルを使うときだけ関係します。H.100通信プロトコルを使わない場合には0にしてください。

C/C++言語用に以下のインターフェースが用意されています。宣言はsysreg.hで行われています。SPx_MCMC2にアクセスする前には必ずIOPGにSPORTx_Control_Pageを設定してください。SPORTはポートごとにIOページが異なりますので注意が必要です。

SPORT0の場合は以下のとおりです。

// #include <sysreg.h> // #include <def2191.h> sysreg_write(sysreg_IOPG, SPORT0_Controller_Page) // SPORT0ページに設定 io_space_write(SP0_MCMC2, 値) // SP0_MCMC2に値を設定 変数 = io_space_read(SP0_MCMC2) // SP0_MCMC2の値を取得

SPORT1の場合は以下のとおりです。

// #include <sysreg.h> // #include <def2191.h> sysreg_write(sysreg_IOPG, SPORT1_Controller_Page) // SPORT1ページに設定 io_space_write(SP1_MCMC2, 値) // SP1_MCMC2に値を設定 変数 = io_space_read(SP1_MCMC2) // SP1_MCMC2の値を取得

SPORT2の場合は以下のとおりです。

// #include <sysreg.h> // #include <def2191.h> sysreg_write(sysreg_IOPG, SPORT2_Controller_Page) // SPORT2ページに設定 io_space_write(SP2_MCMC2, 値) // SP2_MCMC2に値を設定 変数 = io_space_read(SP2_MCMC2) // SP2_MCMC2の値を取得

アナログデバイセズが配布しているmcmの中のビット定義ファイルdef2191bit.hから関連するビット定義部分をここに引用します。

#define FSDR BIT_7 #define MCFF_OFST 5 #define MCFF_MASK ( 3 << MCFF_OFST ) #define MCFF_2CH ( 0 << MCFF_OFST ) #define MCFF_4CH ( 1 << MCFF_OFST ) #define MCFF_8CH ( 2 << MCFF_OFST ) #define MCFF_16CH ( 3 << MCFF_OFST ) #define MCOM BIT_4 #define MCDRXPE BIT_3 #define MCDTXPE BIT_2 #define MCCRM_OFST 0 #define MCCRM_MASK ( 0x03 << MCCRM_OFST ) #define MCCRM_BYPASS ( 0 << MCCRM_OFST ) #define MCCRM_2MHZ ( 2 << MCCRM_OFST ) #define MCCRM_8MHZ ( 3 << MCCRM_OFST )

| 項目 | マニュアルのページ等 |

|---|---|

| レジスタ説明 | HR B-42 |

| マルチチャンネル | HR 9-34 |