SPx_STATR ( SPORTx STATus )レジスタは、シリアルポートの状況を表します。このレジスタは読み出し専用です。

SPORTが3系統あるため、SP0_STATR、SP1_STATR、SP2_STATRの三本が用意されています。

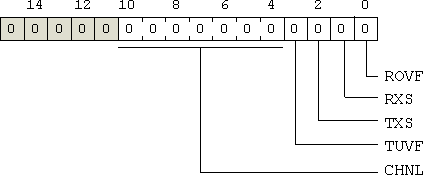

このレジスタは図1のようなビットフィールド構造をもつ16ビットレジスタです。リセット後の値は不定です。

図1 SPx_STATRの構造

以下に各ビットフィールドの説明を行います。詳しくはHRを参照してください。

受信部のオーバーフロー状態を表します。このフラグは一度"1"になるとシリアルポートをディセーブルにするまで"0"に戻りません。

受信バッファの状態を反映します。プロセッサコアがこのフラグを読むたびにアップデートされます。HR B-36にはリセット態が不定とかいてありますが、0の間違いではないでしょうか。あるいはSPORTをイネーブルにしたときに0になるのでしょうか。

送信バッファの状態を反映します。プロセッサコアがこのフラグを読むたびにアップデートされます。HR B-36にはリセット態が不定とかいてありますが、0の間違いではないでしょうか。あるいはSPORTをイネーブルにしたときに0になるのでしょうか。

送信部のアンダーフロー状態を表します。このフラグは一度"1"になるとシリアルポートをディセーブルにするまで"0"に戻りません。

負号なしの7ビット整数フィールドです。この番号はマルチチャンネルモード(TDM)で現在フレーム先頭から何番目のチャンネルが送受信されているかを示します。0が基点です。なお、通常モードとチャンネル選択オフセットモードでは動作が異なることに気をつけてください。

通常モードではフレームの先頭が0であるのに対して、チャンネル選択オフセットモードではオフセットに達したところでチャンネルが0になります。

例えば、オフセットが16でウインドウサイズが8であるとします。通常モードではCHNLに表示される値は0から23であり、これはフレーム先頭からのチャンネル番号を示します。これにたいしてチャンネル選択オフセットモードでは、フレーム先頭から16チャンネル経過したときにCHNLが0になり、ウインドウの末尾で7になります。

C/C++言語用に以下のインターフェースが用意されています。宣言はsysreg.hで行われています。SPx_RXにアクセスする前には必ずIOPGにSPORTx_Control_Pageを設定してください。SPORTはポートごとにIOページが異なりますので注意が必要です。

SPORT0の場合は以下のとおりです。

// #include <sysreg.h> // #include <def2191.h> sysreg_write(sysreg_IOPG, SPORT0_Controller_Page) // SPORT0ページに設定 変数 = io_space_read(SP0_STATR) // SP0_STATRの値を取得

SPORT1の場合は以下のとおりです。

// #include <sysreg.h> // #include <def2191.h> sysreg_write(sysreg_IOPG, SPORT1_Controller_Page) // SPORT1ページに設定 変数 = io_space_read(SP1_STATR) // SP1_STATRの値を取得

SPORT2の場合は以下のとおりです。

// #include <sysreg.h> // #include <def2191.h> sysreg_write(sysreg_IOPG, SPORT2_Controller_Page) // SPORT2ページに設定 変数 = io_space_read(SP2_STATR) // SP2_STATRの値を取得

アナログデバイセズが配布しているmcmの中のビット定義ファイルdef2191bit.hから関連するビット定義部分をここに引用します。

// Definition for SPx_STATR #define SPT_CHNL_OFST 4 #define SPT_CHNL_MASK ( 0x07f << SPT_CHNL_OFST ) #define SPT_TUVF BIT_3 #define SPT_TXS BIT_2 #define SPT_RXS BIT_1 #define SPT_ROVF BIT_0

| 項目 | マニュアルのページ等 |

|---|---|

| レジスタ説明 | HR B-36 |