SPx_TCR ( SPORTx Transmission Control )レジスタは、シリアルポートの送信機能を設定するためのレジスタです。

SPORTが3系統あるため、SP0_TCR、SP1_TCR、SP2_TCRの三本が用意されています。

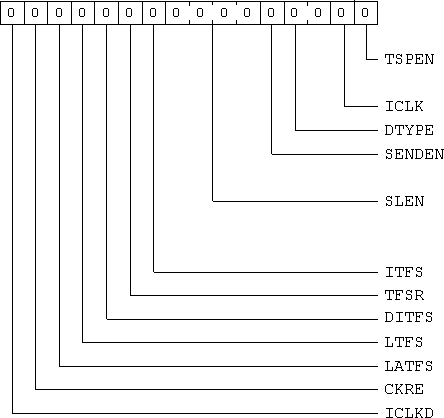

このレジスタは16ビットのレジスタです。リセット後は0に初期化されます。

図1 レジスタの構造

以下に各ビットフィールドの説明を行います。詳しくはHRを参照してください。

SPORTの送信機能を有効にします。

TCLKを内部生成するか決めます。

送信データの型を指定します。

SPORT送信データのエンディアンを指定します。

送信ワード長をビット単位で指定します。0,1を指定してはいけません。Nを指定すると、実際のワード長はN+1になります。最大のNは15なので、最大ワード長は16になります。

フレーム同期を内部生成するよう指定します。

フレーム同期を行うかどうか指定します。マルチチャンネル(TDM)時には0にします。

フレーム同期をデータの有無にあわせて行うか指定します。

フレーム信号の論理を指定します。

フレーム信号の遅延を指定します。マルチチャンネル(TDM)時には0にします。

クロックとデータの関係を指定します。

TCLKをドライブするかどうか指定します。

マルチチャンネル(TDM)でSPORTを使う場合、一部のビットは値を以下のように設定しなければ正しく動きません。

TCLKピンはRCLKピンと接続してください。

C/C++言語用に以下のインターフェースが用意されています。宣言はsysreg.hで行われています。SPx_TCRにアクセスする前には必ずIOPGにSPORTx_Control_Pageを設定してください。SPORTはポートごとにIOページが異なりますので注意が必要です。

SPORT0の場合は以下のとおりです。

// #include <sysreg.h> // #include <def2191.h> sysreg_write(sysreg_IOPG, SPORT0_Controller_Page) // SPORT0ページに設定 io_space_write(SP0_TCR, 値) // SP0_TCRに値を設定 変数 = io_space_read(SP0_TCR) // SP0_TCRの値を取得

SPORT1の場合は以下のとおりです。

// #include <sysreg.h> // #include <def2191.h> sysreg_write(sysreg_IOPG, SPORT1_Controller_Page) // SPORT1ページに設定 io_space_write(SP1_TCR, 値) // SP1_TCRに値を設定 変数 = io_space_read(SP1_TCR) // SP1_TCRの値を取得

SPORT2の場合は以下のとおりです。

// #include <sysreg.h> // #include <def2191.h> sysreg_write(sysreg_IOPG, SPORT2_Controller_Page) // SPORT2ページに設定 io_space_write(SP2_TCR, 値) // SP2_TCRに値を設定 変数 = io_space_read(SP2_TCR) // SP2_TCRの値を取得

アナログデバイセズが配布しているmcmの中のビット定義ファイルdef2191bit.hから関連するビット定義部分をここに引用します。

// Definition for SPx_TCR

// Caution. SLEN 03-16 mean, size of slot is 3-16

// Histry of change : SLENxx->SLEN_xx, added SLEN_OFST,

// SLEN_MASK, DYTPE_OFST, DTYPE_MASK

#define ICLKD BIT_15

#define CKRE BIT_14

#define LATFS BIT_13

#define LTFS BIT_12

#define DITFS BIT_11

#define TFSR BIT_10

#define ITFS BIT_9

#define SLEN_OFST 5

#define SLEN_MASK ( 0x0f << SLEN_OFST )

#define SLEN_3 ( 2 << SLEN_OFST )

#define SLEN_4 ( 3 << SLEN_OFST )

#define SLEN_5 ( 4 << SLEN_OFST )

#define SLEN_6 ( 5 << SLEN_OFST )

#define SLEN_7 ( 6 << SLEN_OFST )

#define SLEN_8 ( 7 << SLEN_OFST )

#define SLEN_9 ( 8 << SLEN_OFST )

#define SLEN_10 ( 9 << SLEN_OFST )

#define SLEN_11 ( 10 << SLEN_OFST )

#define SLEN_12 ( 11 << SLEN_OFST )

#define SLEN_13 ( 12 << SLEN_OFST )

#define SLEN_14 ( 13 << SLEN_OFST )

#define SLEN_15 ( 14 << SLEN_OFST )

#define SLEN_16 ( 15 << SLEN_OFST )

#define SENDN BIT_4

#define DTYPE_OFST 2

#define DTYPE_MASK ( 3 << DTYPE_OFST )

#define DTYPE_ZERO ( 0 << DTYPE_OFST )

#define DTYPE_SIGN ( 1 << DTYPE_OFST )

#define DTYPE_MU ( 2 << DTYPE_OFST )

#define DTYPE_A ( 3 << DTYPE_OFST )

#define ICLK BIT_1

#define TSPEN BIT_0

| 項目 | マニュアルのページ等 |

|---|---|

| レジスタ説明 | HR B-32 |

| SPx_TCR設定 | HR 9-14 |