ADSP-2191のSPORTにはマルチチャンネルモードがあります。マルチチャンネルモードを使うと、一系統のシリアルポートを使って最大128チャンネルの同期データを送受信できます。マルチチャンネルモードではフレーム信号は全チャンネルを送受信するごとに一回だけ生成されるため、このフレームを使って用意にチャンネル同期を取ることができます。

SPx_MRCSy ( SPORTx Multi-Channel Transmit Channel Select y)レジスタは、シリアルポートの受信チャンネルを指定するためのレジスタです(HR ではSPx_MRCSxと表記されていますがここではSPx_MRCSyとします)。yは0から7まであり、16ビットレジスタ8本で128チャンネルを表現します。

SPORTが3系統あるため、SP0_MRCSy、SP1_MRCSy、SP2_MRCSyの三本が用意されています。

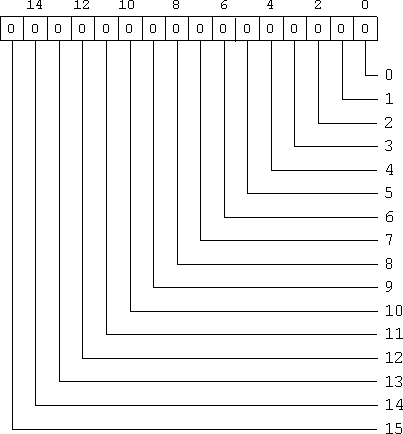

このレジスタは16ビットのビットマップレジスタです。リセット後は0に初期化されます。ビットマップのそれぞれのビットはマルチチャンネル転送時の各チャンネルに対応します。図1はSPx_MRCS0レジスタの構造です。この16ビットレジスタにはチャンネル0からチャンネル15に対応するビットマップが収められています。ビットマップが1のとき、対応するチャンネルはしかるべきタイミングでデータを受信します。ビットマップが0のとき、対応するチャンネルは受信されません。

図1 SPx_MRCS0レジスタの構造

SPx_MRCS1はチャンネル16から31に対応するビットマップを持っています。他のSPx_MRCSyレジスタも同様です。

SPx_MRCSyが実際にどの物理チャンネルに対応するかは、SPx_MCMC1とSPx_MCMC2の設定に依存します。いずれにせよ、SPx_MCMC1で指定するウインドウのなかでだけ送信を行うよう、SPx_MRCSyを設定してください。

DMAを使う場合、SPx_MCM2のMCDRXPEを1にすればSPx_MRCSyで"1"を設定されているチャンネルだけを伝送することができます。この設定はDMA用のバッファメモリを小さくすることができます。

SPx_MRCSyの値はSPORTがイネーブルであっても変更できます。ただし、上で説明したMCDRXPEが1の場合、DMAバッファとチャンネル間の関係がおかしくなります。したがって、SPx_MRCSyを動作中に書き換えるなら、DMAパッキング無しが前提となります。

C/C++言語用に以下のインターフェースが用意されています。宣言はsysreg.hで行われています。SPx_RCRにアクセスする前には必ずIOPGにSPORTx_Control_Pageを設定してください。SPORTはポートごとにIOページが異なりますので注意が必要です。

SP0_MRCS0を使う場合は以下のとおりです。

// #include <sysreg.h> // #include <def2191.h> sysreg_write(sysreg_IOPG, SPORT0_Controller_Page) // SPORT0ページに設定 io_space_write(SP0_MRCS0, 値) // SP0_MRCS0に値を設定 変数 = io_space_read(SP0_MRCS0) // SP0_MRCS0の値を取得

SP0_MRCS0を使う場合は以下のとおりです。

// #include <sysreg.h> // #include <def2191.h> sysreg_write(sysreg_IOPG, SPORT1_Controller_Page) // SPORT1ページに設定 io_space_write(SP1_MRCS0, 値) // SP1_MRCS0に値を設定 変数 = io_space_read(SP1_MRCS0) // SP1_MRCS0の値を取得

SP0_MRCS0を使う場合は以下のとおりです。

// #include <sysreg.h> // #include <def2191.h> sysreg_write(sysreg_IOPG, SPORT2_Controller_Page) // SPORT2ページに設定 io_space_write(SP2_MRCS0, 値) // SP2_MRCS0に値を設定 変数 = io_space_read(SP2_MRCS0) // SP2_MRCS0の値を取得

アナログデバイセズが配布しているmcmの中のビット定義ファイルdef2191bit.hには、チャンネルビットマップ指定用マクロは定義されていません。しかし一般ビットマップ用のマクロがありますのでそれを引用しておきます。

#define BIT_0 0x0001 #define BIT_1 0x0002 #define BIT_2 0x0004 #define BIT_3 0x0008 #define BIT_4 0x0010 #define BIT_5 0x0020 #define BIT_6 0x0040 #define BIT_7 0x0080 #define BIT_8 0x0100 #define BIT_9 0x0200 #define BIT_10 0x0400 #define BIT_11 0x0800 #define BIT_12 0x1000 #define BIT_13 0x2000 #define BIT_14 0x4000 #define BIT_15 0x8000

| 項目 | マニュアルのページ等 |

|---|---|

| レジスタ説明 | HR B-39 |

| SPx_MRCSx設定 | HR 9-35 |