EZ-KIT Lite版のVisualDSP++は、Analog Devicesご自慢の統計的プロファイリングを使ってプログラムの動的振る舞いを調べることができます。

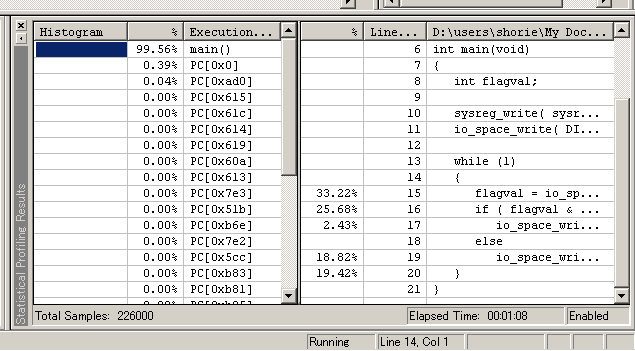

プロファイラを使用するにはプログラムが停止した状態でメニューバー⇒Tools⇒Statistical Profiling⇒Newを実行します。すると空のウインドウが現れます。そこでプログラムを走らせると以下の図の左のようなヒストグラムが現れます。ヒストグラムは関数ごとに全体の何パーセントを占めているか集計したものです。

関数名をダブルクリックするとウインドウの右側にソースコードが表示され、それぞれの行が何パーセントを占めているのか表示します。下のプログラムはPF入力を使おうで使ったプログラムです。走らせながらスイッチを押すと実行行のパーセンテージが変化します。

統計的プロファイリングは実行中のプログラムに影響を与えないため、実時間の挙動をうまく把握できます。最初に高級言語で書いておき、ボトルネックを見極めてから最適化するような手法にぴったりとあいます。反面、この測定値は統計量であること、最適化を施した場合は関数ごとのプロファイルを取れないなどの点は忘れずにいなければなりません。

2002年9月12日現在、VisualDSP++3.0 for 21xxのプロファイラにはidle命令を正しくカウントしないバグがあります。割り込み待ちは普通は次のようなプログラムで実装します。

while (1) asm( "idle;" );

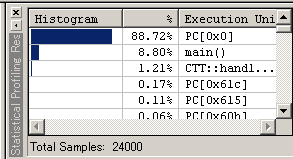

しかしこの方法で割り込みを待っているとVisualDSP++のバグのせいで下の図のような表示になります。

一目見てこの表示がおかしいことがわかります。PC( Program Counter )が0の時間が88.72%と表示されていますが、PC=0はリセット状態です。リセット状態にそんなに頻繁に入るプログラムがまともなわけがありません。この問題を回避するには、現在のところ次のように割り込み待ちのコードを変えるしかありません。

while (1) asm( "nop;" );