FIRフィルターをポリフェーズ分解することによってポリフェーズ・フィルタを作ることができます。ポリフェーズ・フィルタはハードウェアで実現すると通常の実装の位相(Phase)倍の積和演算器が必要となる変わりに、積和演算器に要求される動作速度は小さくなります。ここではもっと鮮烈な応用としてポリフェーズ・フィルタによるレート変換器( Rate Converter )について説明します。

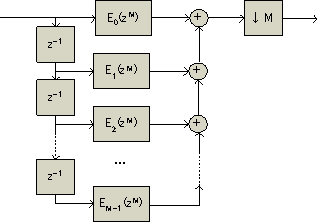

まずはダウン・サンプリングで説明したデシメーターから見てみましょう。図1にデシメーターのブロック図を示します。このデシメーターは入力信号列を1/Mにダウンサンプルします。デシメーションフィルターのインパルス応答はH(z)です。

図1 デシメーター

次にインパルス応答をH(z)=E0 + Z-1E1(ZM) + Z-2E2(ZM) + ... + Z-MEM-1(zM)とポリフェーズ分解します。それが図2です。ポリフェーズ分解後のおのおののフィルタExの係数 Z-xが実際にはZ-1の直列接続であることに注意してください。信号はこの遅延線の中を上から下に流れていきます。ここまででは演算量に大きな変化はありません。Z-xEx(zM)は相変わらず入力周波数と同じレートで動作します。有意な演算はMサンプル毎に1回しか行いませんが、それがM個ありますので帳消しで、実際には遅延線の分だけおそくなります。

図2 デシメーションフィルタのポリフェーズフィルタ化

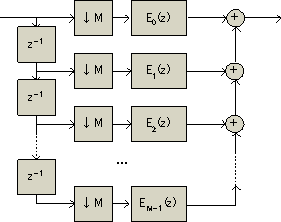

次が一連の変形のなかの最大の山場です。図3ではノーブル恒等変換を利用してダウンサンプラをZ-xEx(zM)の前に移動しています。この変形を行うことで、Z-xEx(zM)の入力周波数は1/Mに落ちます。その結果全体の計算量は1/Mに低下します。これは本来ダウンサンプルの前に行うべき帯域制限を、ノーブル恒等変換を行うことによってダウンサンプル後に行うという魔術的な操作のおかげです。

図3 ノーブル恒等変換による変形

さて、ハードウェアで実装するならば図3で目的は達成しています。この回路のフィルターの動作周波数は図1のデシメーションフィルタの1/Mであり、しかも回路全体の積和総数は図1と同じです。動作周波数が下がって仕事量が同じなのですから回路の負担は大幅に減少します。他方でソフトウエアによる実装面がどうなのかを考えてみましょう。まず実装方法だけかんがえるとこの方式は簡単です。このブロック図はつまるところ図1のデシメーションフィルタでM-1サンプルをためる間は何も出さず、Mサンプルめの入力で一回のフィルター処理をおこない出力を出す方式と同じです。この場合出力のデシメータはいりません。

一方、負荷を考えるとすこし問題があります。すべてのダウンサンプリングを同期して行うため、すべてのフィルタがMサンプル毎に一斉に動作します。その結果、ソフトウェアによる実装では処理がMサンプル毎に集中して行われることになります。また、Mサンプル分の入力データをフィルタに入れる前にどこかのFIFOにためておく必要があります。

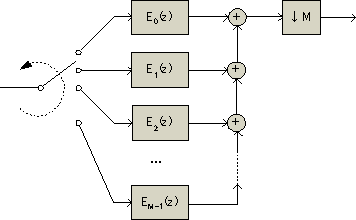

そこでもう一段の変形を施したのが図4です。このブロック図は図4の遅延回路とダウンサンプラをコミュテーター( comuptator )と呼ばれるロータリースイッチで置き換えています。コミュテーターは1サンプル毎に出力をEM-1からE0に切り替えて行きます。各フィルターが1サンプル毎に処理を行います。E0の次は再びEM-1です。この構成では1サンプル毎にh(z)の1/Mのフィルター処理を行いますので、負荷が時間に対して均等に分散されることになります。また、余分な入力FIFOも不必要です。一方でおのおののEx(z)は1サンプル毎にずれた位相で働きますので出力には再びダウンサンプラが必要になります。ただしソフトウエアで書くときにはこのダウンサンプラはE0(z)の計算が終わったときに各フィルタの出力の総和を求めるだけですからきわめて簡単です。

図4 コミュテーターを使った構成

以上のようにポリフェーズフィルタとノーブル恒等変換を利用することでデシメーターに必要な帯域制限フィルタの計算量を1/Mに落とすことができます。

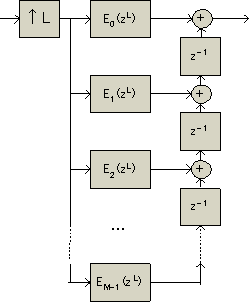

アップ・サンプリングで説明したインターポレーターもポリフェーズフィルタによって計算量を低減することができます。

図5 インターポレーター

インターポレーターもスペクトル抑制用のLPFが周波数が高いほうで動作するために処理が重くなります。そこれでデシメーターと同じようにインターポレーターもポリフェーズフィルター化します。

図6 インターポレーターのポリフェーズ化

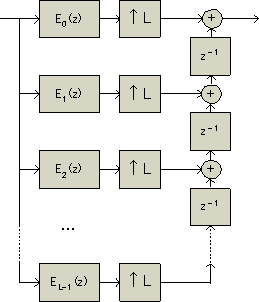

このポリフェーズ化したインターポレーターもノーブル恒等変換を適用することによって動作周波数を落とすことができます。

図7 ノーブル恒等変換を適用

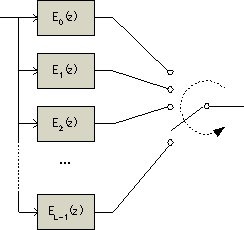

最後にアップ・サンプラと遅延素子をコミュテーターに置き換えることによってソフトウェアの処理を簡易化します。図の上ではE0からEL-1までを同時に演算して結果をコミュテーターで選んでいるように見えます。しかし、それぞれのフィルタの入力はすべて同じサンプルですので、コミュテーターがフィルタのところに来てからそのフィルタの出力を計算してもおなじですし、そのほうが簡単です。

図8 コミュテーターに変換

以上のようにポリフェーズフィルタとノーブル恒等変換を組み合わせることで整数比のレート変換器の動作を大幅に軽くすることができます。これは特に高速なディジタル信号処理で消費電力削減、回路規模削減、不要輻射削減など重要なメリットにつながります。

次は⇒インターポレータの実装