EMICTL( EMI Control )レジスタは外部メモリーへのアクセス方法を制御します。

このレジスタは16ビット整数レジスタです。初期値は0x0060です。

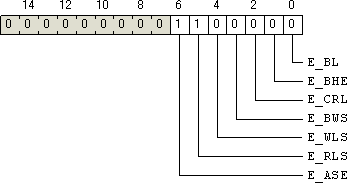

図1 レジスタの構造

バスをロックします。ロック状態ではバスは外部ホストによるバス・リクエストや、外部デバイスによるDMAリクエストに対して許可を与えなくなります。

バスリクエストが行われたとき、16サイクル遅らせてバスを開放します。

MSxCTL、BMSCTL、IOSCTLレジスタへの書き込みをロックします。。

メモリーアクセスバス幅を指定します。

/WRピンの極性を設定します。

/RDピンの極性を設定します。

あるDMAが外部メモリーデバイスのアクセスを長時間待っているときに、他のDMAが内部メモリーアクセスを行ったときの挙動を指定します。

C/C++言語用に以下のインターフェースが用意されています。宣言はsysreg.hで行われています。EMICTLにアクセスする前には必ずIOPGにExternal_Memory_Interface_Pageを設定してください。

// #include <sysreg.h> // #include <def2191.h> sysreg_write(sysreg_IOPG, External_Access_Bridge_Page) // ENIページに設定 io_space_write(EMICTL, 値) // EMICTLに値を設定 変数 = io_space_read(EMICTL) // EMICTLの値を取得

アナログデバイセズが配布しているmcmの中のビット定義ファイルdef2191bit.hから関連するビット定義部分をここに引用します。

//Definition for EMICTL (HR B-93) #define E_ASE BIT_6 #define E_RLS BIT_5 #define E_WLS BIT_4 #define E_BWS BIT_3 #define E_CRL BIT_2 #define E_BHE BIT_1 #define E_BL BIT_0

| 項目 | マニュアルのページ等 |

|---|---|

| レジスタ構造 | HR B-93 |

| 説明 | HR 7-5 |