MSTAT ( Mode Status ) は名前とは裏腹にADSP-2191の動作モードを設定するレジスタです。通常はこのレジスタへの書き込みは行わず、ENA命令とDIS命令を使います。

高級言語からこのレジスタにアクセスすることはまずありません。

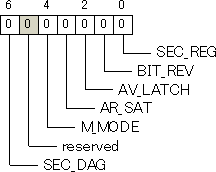

レジスタは7ビット長です。転送命令で16ビットレジスタに格納するときには右詰になります。リセット後の初期値は0です。

MSTATを変更するとADSP-2191の動作モードを変更できます。しかしながら、このレジスタは割り込み時に自動的にスタックに退避されます。したがって、RTI命令を実行すると割り込みハンドラの中で設定したモードはすべて解消されて割り込み前の状態に戻ります。

図1 レジスタの構造

以下に各ビットの概略を説明します。詳細については必ずHRを参照してください。

C/C++言語用に以下のインターフェースが用意されています。宣言はsysreg.hで行われています。

// #include <sysreg.h> sysreg_write(sysreg_MSTAT, 値) // 値をMSTATに代入します 変数 = sysreg_read(sysreg_MSTAT) // MSTATの値を取得します sysreg_bit_clr(sysreg_MSTAT, MASK) // MASKの"1"と対応するMSTATのビットを1にします。 sysreg_bit_set(sysreg_MSTAT, MASK) // MASKの"1"と対応するMSTATのビットを0にします。 sysreg_bit_tgl(sysreg_MSTAT, MASK) // MASKの"1"と対応するMSTATのビットを反転します。 mode_change( __MODE_ENA_AV_LATCH ) // AV_LATCH => 1 mode_change( __MODE_ENA_AR_SAT ) // AR_SAT => 1 mode_change( __MODE_ENA_M_MODE ) // M_MODE => 1 mode_change( __MODE_DIS_AV_LATCH ) // AV_LATCH => 0 mode_change( __MODE_DIS_AR_SAT ) // AR_SAT => 0 mode_change( __MODE_DIS_M_MODE ) // M_MODE => 0

ビットマスクはdef219x.hで定義されています。以下にその部分を引用します。

// #include <def219x.h>

// Bit Positions

#define MSTAT_SEC_REG_P 0 // Bit 0: Secondary data registers enable

#define MSTAT_BIT_REV_P 1 // Bit 1: Bit-reversed address output enable

#define MSTAT_AV_LATCH_P 2 // Bit 2: ALU overflow latch mode select

#define MSTAT_AR_SAT_P 3 // Bit 3: ALU saturation mode select

#define MSTAT_M_MODE_P 4 // Bit 4: MAC result mode select

#define MSTAT_TIMER_P 5 // Bit 5: Timer enable

#define MSTAT_SEC_DAG_P 6 // Bit 6: Secondary DAG registers enable

// Bit Masks

#define MSTAT_SEC_REG MK_BMSK_(MSTAT_SEC_REG_P ) // Secondary data registers enable

#define MSTAT_BIT_REV MK_BMSK_(MSTAT_BIT_REV_P ) // Bit-reversed address output enable

#define MSTAT_AV_LATCH MK_BMSK_(MSTAT_AV_LATCH_P) // ALU overflow latch mode select

#define MSTAT_AR_SAT MK_BMSK_(MSTAT_AR_SAT_P ) // ALU saturation mode select

#define MSTAT_M_MODE MK_BMSK_(MSTAT_M_MODE_P ) // MAC result mode select

#define MSTAT_TIMER MK_BMSK_(MSTAT_TIMER_P ) // Timer enable

#define MSTAT_SEC_DAG MK_BMSK_(MSTAT_SEC_DAG_P ) // Secondary DAG registers enable

MSTATのレイテンシは以下のとおりです。

| 命令 | MSTAT=value; | POP STS; | ENA, DIS | |

|---|---|---|---|---|

| レイテンシ | SEC_REG | 2 | 2 | 1 |

| BIT_REV | 4 | 4 | 1 | |

| AV_LATCH | 1 | 1 | 1 | |

| AR_SAT | 2 | 2 | 1 | |

| M_MODE | 2 | 2 | 1 | |

| SEC_DAG | 4 | 4 | 1 | |

レイテンシが1のとき、直後の命令からその値を使うことができます。レイテンシが2以上のとき、直後の命令でその値を参照しようとすると、古い値を参照します。なお、この表のレイテンシの数え方はHRとは異なっています。

このレジスタにはインターロック機構はついていません。

| 項目 | マニュアルのページ等 |

|---|---|

| ビット割り当て | HR A-10 |

| レイテンシ | HR A-6 |

| 裏データレジスタ | HR 2-57 |

| ビットリバースアドレッシング | HR 4-15 |

| AVラッチモード | HR 2-10 |

| ALU飽和モード | HR 2-11 |

| 裏DAGレジスタ | HR 4-4 |

| "Enabling Interrupt" | ISR 8-14 |