ICNTL ( Interrupt Control ) は割り込み制御レジスタです。割り込み全体の許可/禁止、ネスティングの許可/禁止といった割り込み全体にかかわることや、コア由来の割り込みの許可/禁止を行います。割り込み全般に関しては割り込みの構造も参照してください。

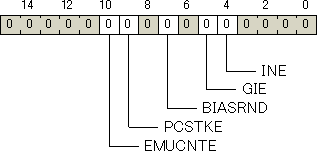

図1にビット配置を示します。初期値は0です。ハーフトーンの部分は予約領域です。予約領域には必ず0を書き込んでください。

図1 レジスタの構造

以下に各ビット概略を説明します。詳細については必ずHRを参照してください。

わんこ蕎麦モードは"spill-fill mode"に対する筆者の勝手な訳です。DSPがわんこ蕎麦状態にあると、SSTATのスタックステータスビットのどれかが1に変化するとスタック割り込みが発生します。スタック割り込みハンドラはこれらの割り込みを受けてスタックの退避/復帰をおこない、あふれやオーバーフローを可能な限り未然に防ぎます。なお、実際に割り込みを起こすにはIMASKのSTACK割り込みマスクが1でなければなりません。

EMUCNTEの詳細は不明です。HR A-18にはこれが割り込みであるという記述はありませんが、索引ではEmulation Countor Interrupt Enableとなっています。おそらくエミュレーションカウンタが一周したときに割り込みが入ると思いますが、どの割り込みが発生するかも記述されていません。実験したところエミュレーション割り込みが入るようです。いずれにせよ64ビット長のこのカウンタが普通に一周することは無いと思いますので心配は無用です(今から走らせて一周するのは西暦52世紀中ごろです)。

GIEはENA INT命令で1になり、DIS INT命令で0になります。ICNTLのGIEを直接いじらず、これらの命令を使うか、下のAPIを使ってください。

C/C++言語用に以下のインターフェースが用意されています。宣言はsysreg.hで行われています。

// #include <sysreg.h> sysreg_write(sysreg_ICNTL, 値) // 値をICNTLに代入します 変数 = sysreg_read(sysreg_ICNTL) // ICNTLの値を取得します sysreg_bit_clr(sysreg_ICNTL, MASK) // MASKの"1"と対応するICNTLのビットを1にします。 sysreg_bit_set(sysreg_ICNTL, MASK) // MASKの"1"と対応するICNTLのビットを0にします。 sysreg_bit_tgl(sysreg_ICNTL, MASK) // MASKの"1"と対応するICNTLのビットを反転します。 mode_change( __MODE_ENA_INT ) // GIE => 1; enable_interrupts() と同じ mode_change( __MODE_DIS_INT ) // GIE => 0; disable_interrupts() と同じ enable_interrupts() // GIE => 1 disalbe_interrupts() // GIE => 0

ビットマスクはdef219x.hで定義されています。以下に引用します。

// Bit Positions #define ICNTL_INE_P 4 // Bit 4: Interrupt nesting mode enable #define ICNTL_GIE_P 5 // Bit 5: Global interrupt enable #define ICNTL_BIASRND_P 7 // Bit 7: MAC biased rounding mode #define ICNTL_PCSTKE_P 10 // Bit 10: PC stack interrupt enable #define ICNTL_CCNTE_P 11 // Bit 11: Cycle counter enable // Bit Masks #define ICNTL_INE MK_BMSK_(ICNTL_INE_P ) // Interrupt nesting mode enable #define ICNTL_GIE MK_BMSK_(ICNTL_GIE_P ) // Global interrupt enable #define ICNTL_BIASRND MK_BMSK_(ICNTL_BIASRND_P) // MAC biased rounding mode #define ICNTL_PCSTKE MK_BMSK_(ICNTL_PCSTKE_P ) // PC stack interrupt enable #define ICNTL_CCNTE MK_BMSK_(ICNTL_CCNTE_P ) // Cycle counter enable

ICNTLのレイテンシは以下のとおりです。

| 命令 | ICNTL=value; | SET/CLR INT | |

|---|---|---|---|

| レイテンシ | 2 | 1 | |

レイテンシが1のとき、直後の命令からその値を使うことができます。レイテンシが2以上のとき、直後の命令でその値を参照しようとすると、古い値を参照します。なお、この表のレイテンシの数え方はHRとは異なっています。

このレジスタにはインターロック機構はついていません。

| 項目 | マニュアルのページ等 |

|---|---|

| ビット割り当て | HR A-18 |

| スタック割り込み | HR 3-37 |

| GIE | HR 3-31 |

| 割り込みの入れ子 | HR 3-32 |