IRPTL ( Interrrupt Latch )レジスタは、IMASKを通ってコアに認識された割り込みを表示します。

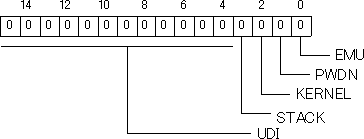

図1にビット配置を示します。初期値は0です。

図1 レジスタの構造

IRPTLはコアに認識され、まだ処理が終わっていない割り込みを表示します。つまりIRPTLに1がたっている割り込みは割り込み処理途中か、割り込みを待っているかです。IRPTLのビットを1にしたり0にすることで、割り込みを強制的に起こしたりクリアすることができます。

いずれのビットも1のとき割り込みが認識されていることを示し、0のときコアが割り込みを認識していないことを示します。各ビットの割り当てはIMASKとまったく同じです。

C/C++言語用に以下のインターフェースが用意されています。宣言はsysreg.hで行われています。

IRPTLは読み書き可能なレジスタですがプログラムによってRead-Modify-Writeを行うと外部から入ってきた割り込みとの間に衝突が起きて、割り込みを失う可能性があります。安全な操作を行うためにSETINT命令とCLRINT命令を使用してください。

// #include <sysreg.h> sysreg_write(sysreg_IRPTL, 値) // 値をIRPTLに代入します 変数 = sysreg_read(sysreg_IRPTL) // IRPTLの値を取得します sysreg_bit_clr(sysreg_IRPTL, MASK) // MASKの"1"と対応するIRPTLのビットを1にします。 sysreg_bit_set(sysreg_IRPTL, MASK) // MASKの"1"と対応するIRPTLのビットを0にします。 sysreg_bit_tgl(sysreg_IRPTL, MASK) // MASKの"1"と対応するIRPTLのビットを反転します。

ビットマスクはdef219x.hで定義されています。以下にその部分を引用します。

// Bit Positions #define INT_EMU_P 0 // Bit 0: Offset: 00: Emulator interrupt #define INT_PWDN_P 1 // Bit 1: Offset: 04: Powerdown interrupt #define INT_KRNL_P 2 // Bit 2: Offset: 08: Kernel interrupt #define INT_STKI_P 3 // Bit 3: Offset: 0c: Stack interrupt #define INT_INT4_P 4 // Bit 4: Offset: 10: Off-Core #define INT_INT5_P 5 // Bit 5: Offset: 14: Off-Core #define INT_INT6_P 6 // Bit 6: Offset: 18: Off-Core #define INT_INT7_P 7 // Bit 7: Offset: 1c: Off-Core #define INT_INT8_P 8 // Bit 8: Offset: 20: Off-Core #define INT_INT9_P 9 // Bit 9: Offset: 24: Off-Core #define INT_INT10_P 10 // Bit 10: Offset: 28: Off-Core #define INT_INT11_P 11 // Bit 11: Offset: 2c: Off-Core #define INT_INT12_P 12 // Bit 12: Offset: 30: Off-Core #define INT_INT13_P 13 // Bit 13: Offset: 34: Off-Core #define INT_INT14_P 14 // Bit 14: Offset: 38: Off-Core #define INT_INT15_P 15 // Bit 15: Offset: 3c: Off-Core // Bit Masks #define INT_EMU MK_BMSK_(INT_EMU_P ) // Offset: 00: Emulator interrupt #define INT_PWDN MK_BMSK_(INT_PWDN_P ) // Offset: 04: Powerdown interrupt #define INT_KRNL MK_BMSK_(INT_KRNL_P ) // Offset: 08: Kernel interrupt #define INT_STKI MK_BMSK_(INT_STKI_P ) // Offset: 0c: Stack interrupt #define INT_INT4 MK_BMSK_(INT_INT4_P ) // Offset: 10: Off-Core #define INT_INT5 MK_BMSK_(INT_INT5_P ) // Offset: 14: Off-Core #define INT_INT6 MK_BMSK_(INT_INT6_P ) // Offset: 18: Off-Core #define INT_INT7 MK_BMSK_(INT_INT7_P ) // Offset: 1c: Off-Core #define INT_INT8 MK_BMSK_(INT_INT8_P ) // Offset: 20: Off-Core #define INT_INT9 MK_BMSK_(INT_INT9_P ) // Offset: 24: Off-Core #define INT_INT10 MK_BMSK_(INT_INT10_P) // Offset: 28: Off-Core #define INT_INT11 MK_BMSK_(INT_INT11_P) // Offset: 2c: Off-Core #define INT_INT12 MK_BMSK_(INT_INT12_P) // Offset: 30: Off-Core #define INT_INT13 MK_BMSK_(INT_INT13_P) // Offset: 34: Off-Core #define INT_INT14 MK_BMSK_(INT_INT14_P) // Offset: 38: Off-Core #define INT_INT15 MK_BMSK_(INT_INT15_P) // Offset: 3c: Off-Core

IRPTLのレイテンシは以下のとおりです。

| 命令 | IRPTL=value; | CLRINT/SETINT n; | |

|---|---|---|---|

| レイテンシ | 1 | 1 | |

レイテンシが1のとき、直後の命令からその値を使うことができます。レイテンシが2以上のとき、直後の命令でその値を参照しようとすると、古い値を参照します。なお、この表のレイテンシの数え方はHRとは異なっています。

このレジスタにはインターロック機構はついていません。

| 項目 | マニュアルのページ等 |

|---|---|

| ビット割り当て | HR A-17 |

| レイテンシ | HR 3-6 |

| 割り込みのラッチ | HR 3-31 |