CACTL ( Cache Control ) はADSP-2191の命令キャッシュを制御する8ビットのレジスタです。キャッシュがどのようにADSP-2191の性能を向上するかについてはDAGページを参照してください。データ転送を行う場合、このレジスタは16ビットデータの中に右詰で配置されます。初期値は0xA0です。

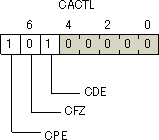

図1にビット配置を示します。ハーフトーンの部分は予約領域です。予約領域には必ず0を書き込んでください。

図1 レジスタの構造

以下に各ビットの概略を説明します。詳細については必ずHRを参照してください。

キャッシュはリセット後有効になっています。とくにいじる必要はありません。なおオーバーレイなどのためにプログラムをPM空間に書き込んだあとには必ずFLUSH命令を実行してキャッシュをクリアしてください。

C/C++言語用に以下のインターフェースが用意されています。宣言はsysreg.hで行われています。

// #include <sysreg.h> sysreg_write(sysreg_CACTL, 値) // 値をCACTLに代入します 変数 = sysreg_read(sysreg_CACTL) // CACTLの値を取得します sysreg_bit_clr(sysreg_CACTL, MASK) // MASKの"1"と対応するCACTLのビットを1にします。 sysreg_bit_set(sysreg_CACTL, MASK) // MASKの"1"と対応するCACTLのビットを0にします。 sysreg_bit_tgl(sysreg_CACTL, MASK) // MASKの"1"と対応するCACTLのビットを反転します。

ビットマスクはdef219x.hで定義されています。以下に引用します。

// Bit Positions #define CACTL_CDE_P 5 // Bit 5: Cache conflicting DM access enable #define CACTL_CFZ_P 6 // Bit 6: Cache freeze #define CACTL_CPE_P 7 // Bit 7: Cache conflicting PM access enable // Bit Masks #define CACTL_CDE MK_BMSK_(CACTL_CDE_P) // Cache conflicting DM access enable #define CACTL_CFZ MK_BMSK_(CACTL_CFZ_P) // Cache freeze #define CACTL_CPE MK_BMSK_(CACTL_CPE_P) // Cache conflicting PM access enable

ICNTLのレイテンシは以下のとおりです。

| 命令 | CACTL=value; | |

|---|---|---|

| レイテンシ | 6 | |

レイテンシが1のとき、直後の命令からその値を使うことができます。レイテンシが2以上のとき、直後の命令でその値を参照しようとすると、古い値を参照します。なお、この表のレイテンシの数え方はHRとは異なっています。

このレジスタにはインターロック機構はついていません。

| 項目 | マニュアルのページ等 |

|---|---|

| ビット割り当て | HR A-22 |

| レイテンシ | HR 3-6 |

| キャッシュについて | HR 3-9 |