SPICTLx( SPI FLAG )はSerial Peripheral Interfaceがマスターモードのときに使用するスレーブセレクトピンを制御するレジスタです。スレーブセレクトを使うことで複数のSPIスレーブデバイスを利用することができます。

SPIが2系統あるため、SPIFLG0, SPIFLG1の2本が用意されています。

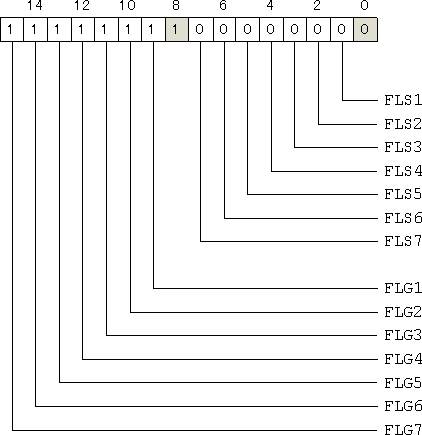

このレジスタは図1のような構造をもっています。初期値は0xFF00です。

図1 レジスタの構造

各ビットの意味は以下のとおりです。

スレーブデバイス選択に使うピンを選びます。

スレーブを選択します。SPICTLxのCPHAが0のとき、FLGxへの書き込みは無視されます( HR 10-15 )。

FLSxはマスクとして働きます。このビットが0の時には、対応するピンはSPIのスレーブセレクトではなくPFピンとして働きます。FLGxは負論理であることに注意してください。

SPIFLG0とSPIFLG1は対応するピンが違います。ピンの割り当てに関してはHR B-56, B-57を参照してください。

C/C++言語用に以下のインターフェースが用意されています。宣言はsysreg.hで行われています。SPIFLGxにアクセスする前には必ずIOPGにSPIx_Controller_Pageを設定してください。

SPIFLG0の場合は以下のとおりです。

// #include <sysreg.h> // #include <def2191.h> sysreg_write(sysreg_IOPG, SPI0_Controller_Page) // SPI0ページに設定 io_space_write(SPIFLG0, 値) // SPIFLG0に値を設定 変数 = io_space_read(SPIFLG0) // SPIFLG0の値を取得

SPIFLG1の場合は以下のとおりです。

// #include <sysreg.h> // #include <def2191.h> sysreg_write(sysreg_IOPG, SPI1_Controller_Page) // SPI1ページに設定 io_space_write(SPIFLG1, 値) // SPIFLG1に値を設定 変数 = io_space_read(SPIFLG1) // SPIFLG1の値を取得

アナログデバイセズが配布しているmcmの中のビット定義ファイルdef2191bit.hから関連するビット定義部分をここに引用します。

// Definition for SPIFLG0 B-56 #define FLS1 BIT_1 #define FLS2 BIT_2 #define FLS3 BIT_3 #define FLS4 BIT_4 #define FLS5 BIT_5 #define FLS6 BIT_6 #define FLS7 BIT_7 #define FLG1 BIT_9 #define FLG2 BIT_10 #define FLG3 BIT_11 #define FLG4 BIT_12 #define FLG5 BIT_13 #define FLG6 BIT_14 #define FLG7 BIT_15

| 項目 | マニュアルのページ等 |

|---|---|

| 説明 | HR B-56, B-57 |

| SPIFLGレジスタ | HR 10-11 |