SPICTLx( SPI Control )はSerial Peripheral Interfaceの設定を行います。ADSP-2191はSPIを2系統持っていますが、ピンはSPORT2と共用です。したがって、SPORT2とSPIデバイスを同時にイネーブルにすることは禁止されています。

SPIが2系統あるため、SPICTL0, SPCTL1の2本が用意されています。

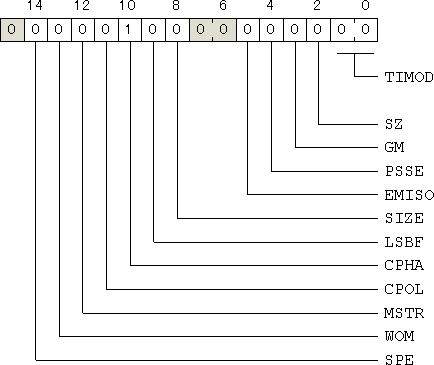

このレジスタは図1のような構造をもっています。初期値は0x0400です。

図1 レジスタの構造

各ビットの意味は以下のとおりです。

SPIデバイスをマスターモードにしているときに、転送を開始するタイミングを設定します。

TDBRが空の状態でデータを送信したときの挙動を指定します。

RDBRが一杯の状態でデータを受信したときの挙動を指定します。

Slave Selectピンを有効にします。

Master In Slave Outピンの設定を行います。

送受信データワード長を指定します。

データワードの送受信方向を決めます。

クロックトグルの方法を指定します。

クロックの極性を指定します。

操作モードを指定します。

送信ピンをオープンドレインにします。

SPIを有効にします。

C/C++言語用に以下のインターフェースが用意されています。宣言はsysreg.hで行われています。SPICTLxにアクセスする前には必ずIOPGにSPIx_Controller_Pageを設定してください。

SPICTL0の場合は以下のとおりです。

// #include <sysreg.h> // #include <def2191.h> sysreg_write(sysreg_IOPG, SPI0_Controller_Page) // SPI0ページに設定 io_space_write(SPICTL0, 値) // SPICTL0に値を設定 変数 = io_space_read(SPICTL0) // SPICTL0の値を取得

SPICTL1の場合は以下のとおりです。

// #include <sysreg.h> // #include <def2191.h> sysreg_write(sysreg_IOPG, SPI1_Controller_Page) // SPI1ページに設定 io_space_write(SPICTL1, 値) // SPICTL1に値を設定 変数 = io_space_read(SPICTL1) // SPICTL1の値を取得

アナログデバイセズが配布しているmcmの中のビット定義ファイルdef2191bit.hから関連するビット定義部分をここに引用します。

// Definition for SPICTLx B-54 #define TIMOD_OFST 0 #define TIMOD_MASK ( 3 << MCCRM_OFST ) #define TIMOD_READ ( 0 << MCCRM_OFST ) #define TIMOD_WRITE ( 1 << MCCRM_OFST ) #define TIMOD_DMA ( 2 << MCCRM_OFST ) #define SZ BIT_2 #define GM BIT_3 #define PSSE BIT_4 #define EMISO BIT_5 #define SIZE BIT_8 #define LSBF BIT_9 #define CPHA BIT_10 #define CPOL BIT_11 #define MSTR BIT_12 #define WOM BIT_13 #define SPE BIT_14

| 項目 | マニュアルのページ等 |

|---|---|

| 説明 | HR B-54 |