DMACR_IRQ ( Memory DMA Channel Read Interrupt )はメモリーDMAのDMA読み出しチャンネルが発生した割り込みをクリアします。

ADSP-2191のコアは内蔵ペリフェラルの割り込みをレベルとして受け付けます。割り込みをクリアするにはペリフェラルごとに割り込み信号を何らかの方法でクリアします。読み出しDMAの場合割り込みをクリアするにはDMACW_IRQのbit1に1を書き込みます。

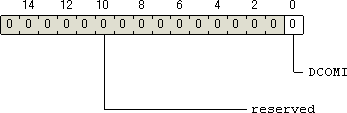

このレジスタは図1のような構造をもっています。初期値は0です。

図1 DMACR_IRQレジスタの構造

各ビットの意味は以下のとおりです。

HRにはこのレジスタには構造がなく、レジスタ全体に"1"を書けばいいように書いています。それはそれで正しいのですが、他のDMA_IRQレジスタとの整合を考えてここでは構造をもつように説明しました。

C/C++言語用に以下のインターフェースが用意されています。宣言はsysreg.hとdef2191.hで行われています。DMACR_IRQにアクセスする前には必ずIOPGにMemory_DMA_Controller_Pageを設定してください。

// #include <sysreg.h> // #include <def2191.h> sysreg_write(sysreg_IOPG, Memory_DMA_Controller_Page) // メモリーDMAページに設定 io_space_write(DMACR_IRQ, 値) // DMACR_IRQに値を設定。 変数 = io_space_read(DMACR_IRQ) // DMACR_IRQの値を取得。

アナログデバイセズが配布しているmcmの中のビット定義ファイルdef2191bit.hから関連するビット定義部分をここに引用します。

// Definition for xxxD_IRQ #define DERI BIT_1 #define DCOMI BIT_0

| 項目 | マニュアルのページ等 |

|---|---|

| 説明 | HR B-31 |

| DMAの解説 | HR 6-1 |

| DMA開始手続き | HR 6-6 |

| DMAメモリー空間 | HR 6-19 |