PLLCTL( PLL Control )はシステムクロックを供給するPLLの制御を行います。PLLの制御は繊細な部分があり、HRを熟読する必要があります。特に逓倍率の変更やパワーダウンへの移行は注意して行ってください。

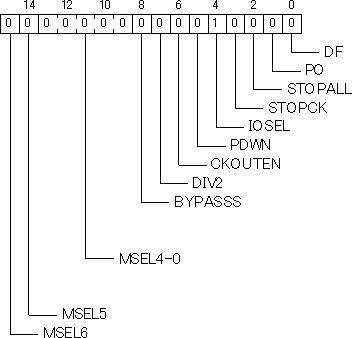

図1にビット配置を示します。初期値は0x0010です。ハーフトーンの部分は予約領域です。予約領域には必ず0を書き込んでください。

図1 レジスタの構造

以下に各ビットの概略を説明します。詳細については必ずHRを参照してください。

PLLの逓倍率を決めます。1-31の値は1-31倍の意味です。0を設定すると32倍になります。

MSEL5=1のときには、必ずDFも1にしてください。

名前が間違っています。これは逓倍ではなく分周を指定します。

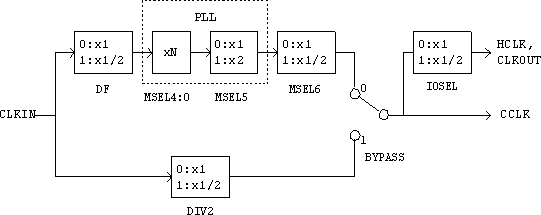

PLL周辺回路の様子はなぜかHRで示されていません。ADSP-2199xのHRを参考にして調べたブロック図を下に示します。PLLの前後にそれぞれ分周器が入っているのを不信に感じるかもしれません。PLLの前の分周器はPLL入力周波数レンジを拡大するためのもので、より高いクロック周波数を許すことでシステム設計の負担を軽くします。一方、MSEL6は低消費電力モードへの以降をすばやく行うものです。MSEL6を使えば即座に周波数を半分にできるので消費電力も半分になります。一方、DFやMSEL4:0、MSEL5を変更するとPLLの動作周波数が変わるため、出力が安定するまでバイパスモードで待機しなければなりません。

バイパスモードはPLLを使わずにCLKINからの入力を直接利用します。PLLを止めれば大幅な消費電力低減を図ることができます。

図2 PLL周辺のブロックダイアグラム

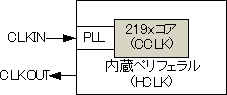

最後にクロック入出力と内部のクロックの配分の様子を図3に示します

図3 PLLとクロックの分配

C/C++言語用に以下のインターフェースが用意されています。宣言はsysreg.hとdef2191.hで行われています。PLLCTLにアクセスする前には必ずIOPGにClock_and_System_Control_Pageを設定してください。

// #include <sysreg.h> // #include <def2191.h> sysreg_write(sysreg_IOPG, Clock_and_System_Control_Page) // クロックページに設定 io_space_write(PLLCTL, 値) // PLLCTLに値を設定 変数 = io_space_read(PLLCTL) // PLLCTLの値を取得

アナログデバイセズが配布しているmcmの中のビット定義ファイルdef2191bit.hから関連するビット定義部分をここに引用します。

#define MSEL6 BIT_15 #define MSEL5 BIT_14 #define MSEL40_OFST 9 #define MSEL40_MASK ( 0x1f << MSEL40_OFST ) #define MSEL40_0 ( 0 << MSEL40_OFST ) #define MSEL40_1 ( 1 << MSEL40_OFST ) #define MSEL40_2 ( 2 << MSEL40_OFST ) #define MSEL40_3 ( 3 << MSEL40_OFST ) #define MSEL40_4 ( 4 << MSEL40_OFST ) #define MSEL40_5 ( 5 << MSEL40_OFST ) #define MSEL40_6 ( 6 << MSEL40_OFST ) #define MSEL40_7 ( 7 << MSEL40_OFST ) #define MSEL40_8 ( 8 << MSEL40_OFST ) #define MSEL40_9 ( 9 << MSEL40_OFST ) #define MSEL40_10 ( 10 << MSEL40_OFST ) #define MSEL40_11 ( 11 << MSEL40_OFST ) #define MSEL40_12 ( 12 << MSEL40_OFST ) #define MSEL40_13 ( 13 << MSEL40_OFST ) #define MSEL40_14 ( 14 << MSEL40_OFST ) #define MSEL40_15 ( 15 << MSEL40_OFST ) #define MSEL40_16 ( 16 << MSEL40_OFST ) #define MSEL40_17 ( 17 << MSEL40_OFST ) #define MSEL40_18 ( 18 << MSEL40_OFST ) #define MSEL40_19 ( 19 << MSEL40_OFST ) #define MSEL40_20 ( 20 << MSEL40_OFST ) #define MSEL40_21 ( 21 << MSEL40_OFST ) #define MSEL40_22 ( 22 << MSEL40_OFST ) #define MSEL40_23 ( 23 << MSEL40_OFST ) #define MSEL40_24 ( 24 << MSEL40_OFST ) #define MSEL40_25 ( 25 << MSEL40_OFST ) #define MSEL40_26 ( 26 << MSEL40_OFST ) #define MSEL40_27 ( 27 << MSEL40_OFST ) #define MSEL40_28 ( 28 << MSEL40_OFST ) #define MSEL40_29 ( 29 << MSEL40_OFST ) #define MSEL40_30 ( 30 << MSEL40_OFST ) #define MSEL40_31 ( 31 << MSEL40_OFST ) #define BYPASS BIT_8 #define DIV2 BIT_7 #define CKOUTEN BIT_6 #define PDWN BIT_5 #define IOSEL BIT_4 #define STOPCK BIT_3 #define STOPALL BIT_2 #define PO BIT_1 #define DF BIT_0

| 項目 | マニュアルのページ等 |

|---|---|

| ビット割り当て | HR B-15 |

| PLL解説 | HR 14-32 |

| パワーダウンモード | HR 14-47 |