IPRx ( Interrupt Priority Register )は、割り込みソースである内蔵デバイスに割り込み優先順位を割り当てます。詳細は割り込みの構造も参照してください。

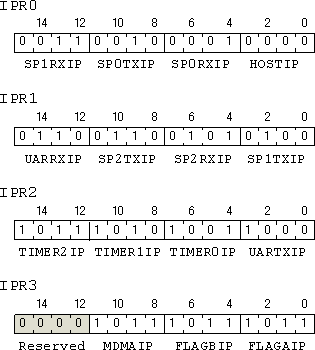

図1にビット配置を示します。初期値はIPR0から順に0x3210, 0x7654, 0xba98, 0xbbbbです。ハーフトーンの部分は予約領域です。

図1 レジスタの構造

それぞれのビットフィールドに入る値は割り込み優先順位ではなく、デバイスの優先順位です。この値に4を足すと、ADSP-2191の割り込み優先順位になります。詳しくは割り込みの構造を参照してください。

C/C++言語用に以下のインターフェースが用意されています。宣言はsysreg.hとdef2191.hで行われています。IPRxにアクセスする前には必ずIOPGにInterrupt_Controller_Pageを設定してください。

// #include <sysreg.h> // #include <def2191.h> sysreg_write(sysreg_IOPG, Interrupt_Controller_Page) // 割り込みページに設定 io_space_write(IPR0, 値) // IPR0に値を設定 変数 = io_space_read(IPR0) // IPR0の値を取得。IPRxも同様

アナログデバイセズが配布しているmcmの中のビット定義ファイルdef2191bit.hから関連するビット定義部分をここに引用します。

// Definition of IPR0 #define SP1RXIP_OFST 12 #define SP1RXIP_MASK 0xf000 #define SP0TXIP_OFST 8 #define SP0TXIP_MASK 0x0f00 #define SP0RXIP_OFST 4 #define SP0RXIP_MASK 0x00f0 #define HOSTIP_OFST 0 #define HOSTIP_MASK 0x000f // Definition of IPR1 #define UARRXIP_OFST 12 #define UARRXIP_MASK 0xf000 #define SP2TXIP_OFST 8 #define SP2TXIP_MASK 0x0f00 #define SP2RXIP_OFST 4 #define SP2RXIP_MASK 0x00f0 #define SP1TXIP_OFST 0 #define SP1TXIP_MASK 0x000f // Definition of IPR2 #define TIMER2IP_OFST 12 #define TIMER2IP_MASK 0xf000 #define TIMER1IP_OFST 8 #define TIMER1IP_MASK 0x0f00 #define TIMER0IP_OFST 4 #define TIMER0IP_MASK 0x00f0 #define UARTXIP_OFST 0 #define UARTXIP_MASK 0x000f // Definition of IPR3 #define MDMAIP_OFST 8 #define MDMAIP_MASK 0x0f00 #define FLAGBIP_OFST 4 #define FLAGBIP_MASK 0x00f0 #define FLAGAIP_OFST 0 #define FLAGAIP_MASK 0x000f

| 項目 | マニュアルのページ等 |

|---|---|

| ビット割り当て | HR B-21 |

| 割り込みの解説 | HR 3-25 |

| 割り込み順位 | HR C-1 |