HPCR( Host Port Configuration Register )偼儂僗僩億乕僩偺愝掕傪曄峏偡傞偨傔偺儗僕僗僞偱偡丅

偙偺儗僕僗僞偼16價僢僩儗僕僗僞偱偡丅弶婜抣偼0x0000偱偡丅

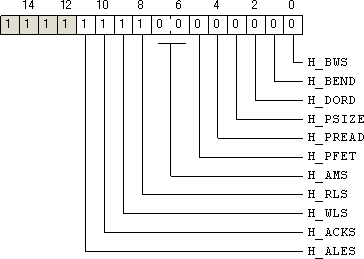

恾1 儗僕僗僞偺峔憿

僶僗暆傪巜掕偟傑偡丅

僶僗暆偑僨乕僞暆傛傝抁偄偲偒偵丄僄儞僨傿傾儞傪巜掕偟傑偡丅

僶僗暆偑僨乕僞暆傛傝抁偄偲偒偵丄揮憲弴彉傪巜掕偟傑偡丅

僶僗暆偑8價僢僩偱揮憲僨乕僞暆偑24價僢僩偺偲偒丄揮憲偵巊梡偡傞僷働僢僩悢傪巜掕偟傑偡丅

僷僀僾儔僀儞丒儌乕僪偱偼丄暋悢僷働僢僩揮憲偵偍偄偰2夞栚埲崀偺僷働僢僩揮憲偼幚嵺偵儂僗僩偑撉傒弌偟傪偐偗傞慜偵撪晹儊儌儕乕偺撉傒弌偟傪峴偄傑偡丅

H_PRED偲H_PFET傪摨帪偵1偵偟偰偼偄偗傑偣傫丅

僾儕僼僃僢僠丒儌乕僪偱偼傾僪儗僗偑梌偊傜傟傞偲幚嵺偵儂僗僩偑僨乕僞撉傓傛傝傕慜偵撪晹儊儌儕乕偺撉傒弌偟傪峴偄傑偡丅

H_PRED偲H_PFET傪摨帪偵1偵偟偰偼偄偗傑偣傫丅

ACK怣崋偺嬌惈側偳傪寛傔傑偡丅徻偟偔偼HR B-103偺Table B-13傪嶲徠偟偰偔偩偝偄丅

/RD偺忬懺傪挷傋傑偡(RO)

/WR偺忬懺傪挷傋傑偡(RO)

/ACK偺忬懺傪挷傋傑偡(RO)

/ALE偺忬懺傪挷傋傑偡(RO)

C/C++尵岅梡偵埲壓偺僀儞僞乕僼僃乕僗偑梡堄偝傟偰偄傑偡丅愰尵偼sysreg.h偱峴傢傟偰偄傑偡丅HPCR偵傾僋僙僗偡傞慜偵偼昁偢IOPG偵External_Memory_Interface_Page傪愝掕偟偰偔偩偝偄丅

HPCR偵傾僋僙僗偡傞応崌偼師偺傛偆偵惉傝傑偡丅

// #include <sysreg.h> // #include <def2191.h> sysreg_write(sysreg_IOPG, Host_Port_Bus_Interface_Page) // HPI儁乕僕偵愝掕 io_space_write(HPCR, 抣) // HPCR偵抣傪愝掕 曄悢 = io_space_read(HPCR) // HPCR偺抣傪庢摼

傾僫儘僌僨僶僀僙僘偑攝晍偟偰偄傞mcm偺拞偺價僢僩掕媊僼傽僀儖def2191bit.h偐傜娭楢偡傞價僢僩掕媊晹暘傪偙偙偵堷梡偟傑偡丅

// Definition for HPCR (HR B-101) #define H_ALES BIT_11 #define H_ACKS BIT_10 #define H_WLS BIT_9 #define H_RLS BIT_8 #define H_AMS_OFST 6 #define H_AMS_MASK ( 0x3 << H_AMS_OFST ) #define H_AMS_ACK ( 0 << H_AMS_OFST ) #define H_AMS_READY ( 1 << H_AMS_OFST ) #define H_PFET BIT_5 #define H_PRED BIT_4 #define H_PSIZE BIT_3 #define H_DORD BIT_2 #define H_BEND BIT_1 #define H_BWS BIT_0

| 崁栚 | 儅僯儏傾儖偺儁乕僕摍 |

|---|---|

| 儗僕僗僞峔憿 | HR B-102 |

| 愢柧 | HR 8-5 |