L1メモリ

L1メモリはプロセッサ・コアに一番近い位置に配置されている高速のメモリです。Blackfinはプログラミング・モデルとしては単一の32GBアドレス空間を扱いますが、高速信号処理のためにL1メモリは命令とデータに別れています。

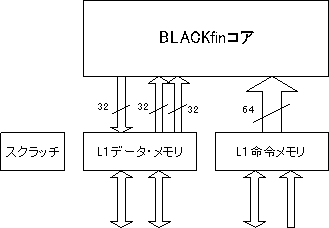

BlackfinコアとL1メモリの構成を図1に示します。Blackfinは製品によってL1メモリのサイズが異なりますが、構成はほとんど変わりません。この図ではデータバスだけを描き、アドレスバスは描いていません。

図1 BlackfinコアとL1メモリ

L1命令メモリとコアの間は64ビットのフェッチ・バスで結ばれています。命令L1メモリの反対側にはL2メモリから命令を読み出すバースト・アクセス・バスとDMAバスが接続されています。なお、ADSP-BF533にはL2メモリがないため、バースト・アクセス・バスは接続されていません。L1命令メモリはこれらのバスに対して擬似マルチポート・メモリとして働きます。

L1データ・メモリとコアの間はもっと複雑です。ここには32ビットのロード・バスが2系統とストア・バスが1系統あります。これらを使ってBlackfinはデュアル・ロード、あるいはロード&ストアを1サイクルで行うことができます。デュアル・ストアはできません。L1データ・メモリにもバースト・アクセス・バスとDMAバスが接続されています。BF533にはL2メモリがありませんのでL1データ・メモリのバースト・アクセス・バスも接続されていません。L1データ・メモリも擬似マルチポート・メモリとして働きます。

スクラッチ・メモリはやや特殊な位置にあります。上の図では省略していますがデータL1メモリ同様コアとの間はストア・バスおよびロード・バスと接続されています。L1データ・メモリと異なるのはバースト・アクセス・バスとDMAバスが接続されていないことです。

このようにBlackfinのL1メモリはやや複雑な構成になっています。これらを使い分けることでBlackfinの最大性能を引き出すわけですが、その前にもう少しL1メモリの構造を理解する必要があります。